# Analyzing the performance of Cascaded H-Bridge Multilevel Inverter with three phase multiwinding transformer and single phase supply

## P.Kathirvel<sup>1</sup>, V.Karpagam<sup>2</sup>, K.Vijayakumar<sup>3</sup>, A.Venkatesh<sup>4</sup>

<sup>1</sup>P.Kathirvel, Assistant Professor, Department of EIE, Dr.Mahalingam College of Engg & Tech, Pollachi, Tamilnadu.

<sup>2</sup>V.Karpagam, Assistant Professor(SS), Department of EIE, Dr.Mahalingam College of Engg & Tech, Pollachi, Tamilnadu.

<sup>3</sup>Dr.K.Vijayakumar, Associate Professor, Department of EIE, Dr.Mahalingam College of Engg & Tech, Pollachi, Tamilnadu

<sup>4</sup>A. Venkatesh, Assistant Professor, Department of EIE, Dr. Mahalingam College of Engg & Tech, Pollachi, Tamilnadu

**Abstract** - In this article, a cascaded H-bridge type multilevel inverter design is propose with a different harmonic reduction technique and multiwinding transformer. The proposed design includes the DC source, hybrid cascaded multilevel inverter, transformer and load circuit. Hybrid cascaded multilevel inverter is obtained Seven-level stepped waveform near sine wave and also increases the efficiency of the multilevel inverter. The seven level hybrid cascaded multilevel inverter fed to the load through the transformer. The algorithm was able to efficiently eliminate fifth and seventh harmonics from line current. Simulation and experiments were performed to show the proposed method work in practice. The observed harmonic detail results, it can be exhibit that the Total Harmonic Distortion is approximately 12.27% only. The 3<sup>rd</sup> level harmonics magnitude is 5.2% and 5<sup>th</sup> level harmonics is only 8.2%. Simulation results from SIMULINK/MATLAB software and hardware experimental results are tabulated. The results are explained with graphically.

**Index Terms** - Multilevel inverter, Single phase DC link, Total Harmonic distortion (THD), Flying capacitors, Linear load.

### 1. INTRODUCTION

The Multilevel converters have created an important rule from various applications. Also, it can be used in renewable energy sources where the above multilevel converters used as a power link about the renewable sources, like Wind, Solar, Hydro, Biomass, and waste & Bagasse, photovoltaic modules from one side and opposite side high-power loads. One of the basic and wellknown topologies among all multilevel inverters is Cascaded H-Bridge Multilevel Inverter. It can be used for both single and three phase conversion. It uses H-Bridge including switches and diodes. At least three voltage levels are required for a multilevel inverter.

The converters have a variety of switches and capacitors voltage sources. By a turn on and turn off control of the power MOSFET switches, the device can generate stepped output voltages with less harmonic distortions. multilevel inverters are used manufacturing factories and government electricity board as one of the new power converter fields because they can manage the drawbacks of traditional Pulse Modulation (PWM) inverters [6][11]. It can be classified into three different types like Diodeclamped, Flying type capacitors and Cascaded H-bridge cells with separate dc sources [7].

#### 1.1 DIODE CLAMPED TYPE INVERTER

The diode clamped inverter is used diodes and give the multiple voltage levels through the various phases values to the capacitor banks where they are connected in series. Diodes send the fixed value of voltage, so reducing the pressure on other electrical devices. The maximum output voltage is 50% of the input DC voltage. Hence this type of problem can be resolved by increasing the switches, diodes, capacitors in the circuit. Due to the capacitor matching issues, these are limited to the three levels and checking the steadiness of each dc-link voltage of the capacitor terminal [1][8].

# 1.2 FLYING TYPE CAPACITOR INVERTER

It is of series connection of capacitor clamped switching diodes. The capacitors transfer the limited amount of voltage to electrical devices. The switching states are like in the diode clamped inverter. Clamping diodes are not required in this type of multilevel inverters. The output is half of the input DC voltage.

# 1.3 CASCADED H-BRIDGE CELLS WITH SEPARATE DC SOURCES

The new cascaded H-bridge-type multilevel inverter, every low-voltage H-bridge module has a separate dc-link voltage source [1][7]. This type of inverter is differently used capacitors and MOSFET switches and requires less number of components in each level. It has some drawback of the similar dc-link voltage needs to be delivered by each H-bridge unit separately [4]. To reduce the number of independent de sources replacing reactors or capacitors were inserting in the new products; however, they also need at least three independent sources. The Bidirectional switch method has been introduced to find the different between the input and the output; although it requires one input source, it produces a complex circuit configuration because of its use of the bidirectional switches.

## 2. CASCADED H-BRIDGE MULTILEVEL INVERTER

multilevel H-bridge Cascaded requires one single dc input power source and three different three-phase low-frequency transformers. By the proposed design, a number of transformers can be reduced, compared traditional three-phase with multilevel single-phase inverters using simple and transformers. Therefore, an efficient inverter can be designed. The relay angles of each switch are calculated by the Newton-Raphson method on the basis operation of each switch. All relay angles can be calculated by using the linearization method to each area. This method is useful to remove the low harmonic components of the output voltage [3].

The cascaded multilevel inverter is promising power electronics topology [2] for high-power because applications of its electromagnetic interference (EMI) and high efficiency low-switching-frequency with control method [6]. Conventionally, each phase of a cascaded multilevel inverter requires n- DC sources for 2n + 1 level. For many applications, obtaining so many separate dc sources may preclude the use of such an inverter. To reduce the number of DC sources required when the cascaded H-bridge multilevel inverter is applied to a different motor drive, that permits the use of a single dc-source as the first DC source with the remaining (n -1)-DC sources has capacitors in the cascaded H-bridges multilevel inverter, which is referred to as the hybrid cascaded Hbridge multilevel inverter (HCMLI) [4].

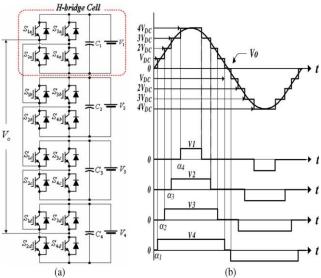

Fig. 2.1 shows a circuit configuration of a traditional cascaded H-bridge type multilevel inverter with four different H-Bridges cell [9]. It provides a nine-level output voltage. The output voltage is a low voltage which is produced by series-connected H-bridge cells.

# 2.1 WORKING PRINCIPLE OF HYBRID CASCADED MULTILEVEL INVERTER (HCMLI)

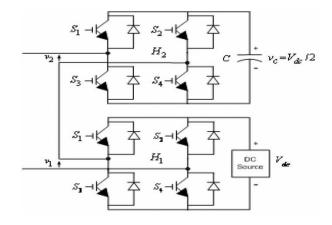

To operate a cascaded multilevel inverter (CMLI) using a single DC source, capacitors are used as the DC sources for all but the first source [3]. Make a cascaded type multilevel inverter with two H-bridges as shown in Fig. 2.1. The DC source for the starting H-bridge is a battery or fuel cell with an output voltage of  $V_{dc}$ , while the dc source for the next H-Bride is a capacitor whose voltage is to be held at  $V_c$ . The final voltage of the starting H-bridge is  $V_1$  and the output of the next H-bridge is  $V_2$ , hence the final voltage of the cascaded type multilevel inverter is

$$v(t_f) = v_1(t_s) + v_2(t_n)$$

(2.1)

Fig 2.1 Traditional 9 –level cascaded type H-bridge cell multilevel inverter

(a) Circuit diagram (b) output waveforms.

By turn-on and turn-off the switches of starting bridge appropriately, the output voltage  $v_1$  can be made equal to  $-V_{dc}$ , 0, or  $V_{dc}$ , with the next output voltage of next bridge can be equal to  $-V_c$ , 0, or  $V_c$  by turn-off and turn-on its switches appropriately. Therefore, the final voltage of the inverter can have the values  $-(V_{dc} + V_c)$ ,  $-V_{dc}$ ,  $-(V_{dc} - V_c)$ ,  $-V_c$ , 0,  $V_c$ ,  $(V_{dc} - V_c)$ ,  $V_{dc}$ , and  $(V_{dc} + V_c)$  which constitute nine different final levels. To maintain the capacitor's voltage, make all

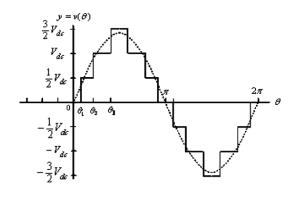

the possible voltage levels must be used in a cycle. A simple 7-level final voltage case  $-3V_{dc}/2$ ,  $-V_{dc}$ ,  $-V_{dc}/2$ , 0,  $V_{dc}/2$ , Vdc,  $3V_{dc}/2$  can be designed, in Fig. 2.3, when the capacitor's voltage Vc is make as  $V_{dc}/2$ . The final values shows in the Fig. 2.2 and table 2.1

Fig. 2.2 1ø Multilevel Inverter

Fig. 2.3. 7- Different level 1- Step same Voltage Waveform

Table 2.1 Output voltages for a sevenlevel inverter

| θ                                  | V1              | V2              | $V = V_1 + V_2$ |

|------------------------------------|-----------------|-----------------|-----------------|

| $0 \le \theta \le \theta_1$        | 0               | 0               | 0               |

| $\theta_1 \le \theta \le \theta_2$ | 0               | <u>V</u> 4e/2   | <u>V</u> 45/2   |

| $\theta_1 \le \theta \le \theta_2$ | V <sub>ds</sub> | - <u>V</u> 45/2 | <u>V</u> 4./2   |

| $\theta_2 \le \theta \le \theta_3$ | V <sub>ds</sub> | 0               | V <sub>de</sub> |

| $\theta_1 \le \theta \le \pi/2$    | V <sub>ds</sub> | <u>V4</u> ./2   | 3Vdc/2          |

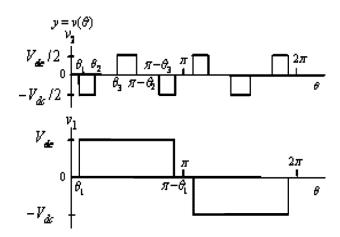

Fig.2.4 H-Bridge Voltages V<sub>1</sub> And V<sub>2</sub>

Control

Fig. 2.4 shows H-bridge voltages  $v_1$  and  $v_2$  control for  $\theta_1 \le \theta < \theta_2$ ,  $v_1 = V_{dc}$  and  $v_2 = -V_{dc}/2$  and how the waveform of Fig. 2.3 is generated if for  $\theta_1 \le \theta < \theta_2$ ,  $V_1 = V_{dc}$  and  $V_2 = -V_{dc}/2$  are chosen.

## 3. MODULATION CONTROL

The PWM control methods and space vector PWM methods are used to multilevel-inverter modulation control. These methods will produce the extra-losses due to fast switching frequencies [8]. So that, the low-switching frequency control methods, such as selective harmonic elimination method, fundamental frequency switching method or active harmonic elimination method can be used for the HCMLI control. From the proposed work the fundamental frequency method is used [5].

# 3.1 SEVEN LEVEL EQUAL STEP OUTPUT VOLTAGE SWITCHING CONTROL

The Fourier series expansion of the 7-level equal step output voltage waveform shown in Fig. 2.4 is

$$V(wt) = \sum_{n=1,3,5}^{\infty} \frac{2Vdc}{n\pi} \left( \left( cosn\theta \ 1 + cosn\theta \ 2 + cosn\theta \ 3 \right) \right) \left( sin(mwt) \right)$$

(2.2)

Where n is the harmonic number of the output voltage of the multilevel inverter [7]. Similarly, given a desired fundamental voltage V1, one wants to determine the switching angles  $\theta_1$ ,  $\theta_2$ , and  $\theta_3$  so that V ( $\omega$ t) = V1  $\sin(\omega t)$ , and specific higher harmonics of V ( $n\omega t$ ) are eliminated. In this project, the objective is to reach the fundamental and eliminate the fifth and seventh harmonics. Using (2.2), this can be formulated as the solution to the following equations:

$$\cos(\theta_1) + \cos(\theta_2) + \cos(\theta_3) = m \tag{2.3}$$

$$\cos(5\theta_1) + \cos(5\theta_2) + \cos(5\theta_3) = 0$$

(2.4)

$$\cos(7\theta_1) + \cos(7\theta_2) + \cos(7\theta_3) = 0$$

(2.5)

The proposed model of three inspirational equations in the three unknown's  $\theta_1$ ,  $\theta_2$ , and  $\theta_3$ .

# 3.2 FEATURES OF HYBRID CASCADED MULTILEVEL INVERTER

The main features are as follows:

- For electric power AC converted to DC Power, the cascaded inverters require single dc link sources. It can use only Selective Harmonic Elimination PWM (SHEPWM) technique. It needs new design of dc link sources to use in different renewable energy sources such as fuel cell and biomass.

- To make connection between the dc link sources and converters in a consecutive mode is not likely because a short circuit can be presented in between the switching synchronization.

# 3.3 ADVANTAGES OF HYBRID CASCADED MULTILEVEL INVERTER

The major advantages of the cascaded inverter can be summarized as follows:

• Compared with the diode-clamped and flying-capacitors inverters, it needs less number of components to achieve the same output voltage levels.

- All the circuit configuration and components are promising since every level has the same configuration and they no need extra clamping diodes or voltage-balancing capacitors.

- Different soft switching techniques are required to reduce the switching voltage drops and device stresses.

# 4. PROPOSED CASCADED H-BRIDGE MULTILEVEL INVERTER WITH MULTIWINDING TRANSFORMER

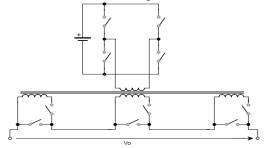

The multi winding-transformer topology can be considered as a variation of the multiplesource topology. A four-cell multi winding inverter is shown in Fig. 4.1

Fig 4.1 symbol of multi-winding transformer

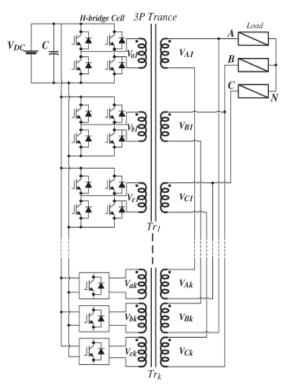

## 4.1 CIRCUIT CONFIGURATION

Fig. 4.2 displays a circuit design of the new multilevel inverter for three-phase supply [2]. It has a one single dc input source and several three-phase output low-frequency transformers. By using the three-phase transformers, the number of required components and the volume of system can be reduced. The primary side of the transformer is connected to an H-bridge input so as to synthesize V<sub>DC</sub>, zero, and -V<sub>DC</sub>. The secondary side of the transformer is connected in series with the output level up. The 3-phase terminal is delta connected to restrain the 3<sup>rd</sup> harmonic component of the system.

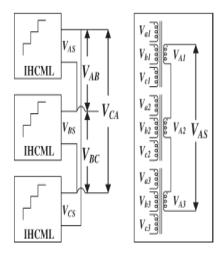

Fig. 4.3 shows a representation of Fig. 4.2 show the three-phase transformers. The three terminal outputs are serially connected to produce the voltage  $V_{AS}$ . In this given design, each phase can be conveyed individually, and all the phase multilevel inverter as isolated H-

bridge cascaded multilevel inverter. In Fig. 4.2, Vak, Vbk, and Vck mean the final voltages of the H-bridge inverter connected to the kth transformer. So the VAk, VBk, and VCk are the final voltages of the three transformers in each phase values [9].

Fig 4.2 the given design of multilevel inverter

Fig 4.3 the minimized design of the given multilevel inverter

# 5. HARMONIC REDUCTION TECHNIQUE

There are four equations to find the angles to reduce LOH especially 5<sup>th</sup>, 7<sup>th</sup> and 11<sup>th</sup> in the output voltage. At the same time we can control the required output RMS voltage using the equation 2.2. The other equations are used to reduce the fifth, seventh and eleventh order harmonics. Totally the THD is reduced.

The four equations are

$Cos\alpha_1+Cos\alpha_2+Cos\alpha_3+Cos\alpha_4 = 3\pi m$

$Cos5\alpha_1+Cos5\alpha_2+Cos5\alpha_3+Cos5\alpha_4=0$

$Cos7\alpha_1+Cos7\alpha_2+Cos7\alpha_3+Cos7\alpha_4=0$

$Co115\alpha_1+Cos11\alpha_2+Cos11\alpha_3+Cos11\alpha_4 = 0$

Using MathCAD program, the conduction angles were found to satisfy the above equations and they are

$$\alpha_1 = 12.834^\circ$$

;  $\alpha_2 = 29.908^\circ$ ;  $\alpha_3 = 50.993^\circ$ ;  $\alpha_4 = 64.229^\circ$ ;

The total harmonic distortion is defined as

THD =

$$\sqrt{(V_3^2 + V_5^2 + V_7^2 + \dots V_{31}^2)}$$

First the transcended equations are converted into polynomials. Then the variables are taken to form the four equations. Consider Cos  $\theta_i = x_i$ ;

Cos

$$(5\theta)$$

=  $5\cos\theta - 20\cos^3\theta + 16\cos^5\theta$

Cos  $(7\theta)$  =  $-7\cos\theta + 56\cos^3\theta - 112\cos^5\theta + 64\cos^7\theta$

Cos  $(11\theta)$  =  $-11\cos\theta + 220\cos^3\theta - 1232\cos^5\theta + 2816\cos^7\theta - 1024\cos^{11}\theta$

The polynomials are formed by

$P_1(x) = x_1 + x_2 + x_3 + x_4 - m$

$P_2(x) = \sum_{i=1, 5,7,11} (5x_i - 20x_i^3 + 16x_i^5)_{i=1, 5,7,11}$

$P_3(x) = \sum_{i=1, 5,7,11} (-7x_i + 56x_i^3 - 112x_i^5 + 64x_i^7)_{i=1, 5,7,11}$

$P_4(x) = \sum_{i=1, 5,7,11} (-11x_i + 220x_i^3 - 1232x_i^5 + 2816x_i^7 + 1024x_i^{11})_{i=1, 5,7,11}$

This is a set of four equations in the four unknown's. Further, the solutions must satisfy all equations. This development has resulted in a set of polynomial equations rather than trigonometric equations. Though the degree is high, there is a well-known theory to solve sets of polynomial equations. The resultant theory is used to solve these set of equations.

After the MathCAD program, the final solution is  $\alpha_1 = 12.834^\circ$ ;  $\alpha_2 = 29.908^\circ$ ;  $\alpha_3 = 50.993^\circ$ ;  $\alpha_4 = 64.229^\circ$ ; these angles reduce the Total Harmonic Reduction in the output voltage.

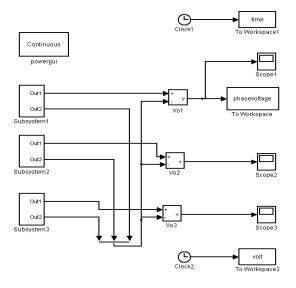

#### 6. SIMULINK MODEL OF CMLI

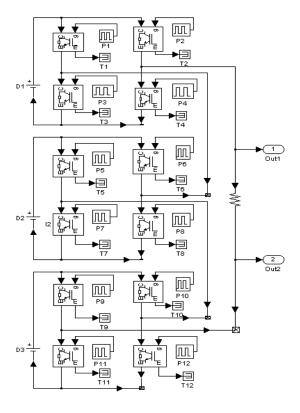

Fig.5.1 proposed simulation design of 3ø-CMLI

Fig. 5.1 shows proposed simulation design of 3ø CMLI. This design consists of three different subsystems. The each subsystem block represents a subsystem of the system that contains it. The each subsystem to group blocks together in our design to reduce design complexity. Each subsystem blocks having the 7- level CMLI. The voltage values of the each subsystem are done by voltage measurement unit.

#### 5.1 SUBSYSTEM MODEL OF CMLI

Fig. 5.2 Subsystem model of CMLI

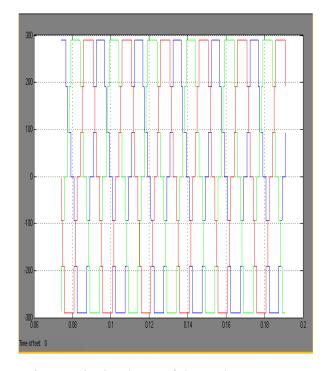

## **5.2 OUTPUT VOLTAGE**

The Fig 5.3 displays the final voltage values of simulated three phases CMLI for the input voltage of 110V. The final voltage of all blocks consists of 110V and the total peak to peak voltage of 330V.

Fig 5.3 Final voltage of three phase CMLI

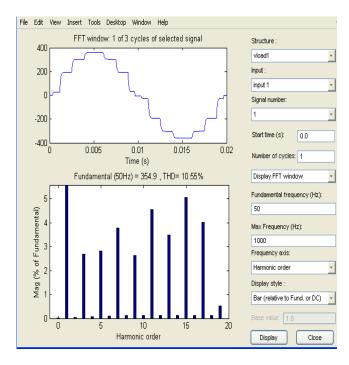

#### **5.3 HARMONIC PROFILE**

The Fig 5.4 shows the all harmonic levels of the seven level cascaded MLI.

Fig 5.4 Harmonic level of the seven level CMLI.

It waveform shows that the total harmonic distortion (THD) is 9.55%. The 3<sup>rd</sup> order

harmonics magnitude is 2.0% and 5<sup>th</sup> order harmonics is around 2.3%.

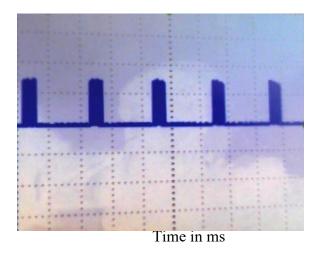

To experimentally validate the proposed HCMLI with seven level equal-step output-voltages, a prototype single-phase-cascaded H-bridge multilevel inverter has been built using MOSFETs as the switching devices. Single dc power supply feed the inverter. The controlled gate signals are given as input to the MOSFET. At that time the pulse of the first H-bridge positive leg pair MOSFET is shown in Figure 7.1 as, during this gate Pulse is applied to M<sub>1</sub> and M<sub>2</sub>.

Figure 5.5 Pulse Width of MOSFET (M<sub>1</sub> and M<sub>2</sub>)

#### 6. CONCLUSION

The proposed hybrid cascaded multilevel inverter develops a cascaded multilevel inverter. Hybrid cascaded multilevel inverter is obtained Seven-level stepped waveform near sine wave and also increases the efficiency of the multilevel inverter. The seven level hybrid cascaded multilevel inverter fed to the load has been illustrated in simulation results by using MATLAB. In hardware implementation of seven-level hybrid cascaded multilevel inverter output phase voltage is given to load and output phase voltage compared to simulation output phase voltage.

The different modern power electronics equipment is produce periodic and large in higher harmonics. They are called as frequencies and also above the bandwidth of regulators used to manage the initial components. Therefore, regular controlling techniques can control the somewhat minimize their effects on the distortion of control variables. The HCMI uses only one power source for each phase while generating desired multilevel voltage waveforms. In this project, the calculation time is insensitive to the switching frequency ratio and the stepped waveform had minimal total harmonic distortion. The fifth and seventh order harmonics are reduced by using the harmonic elimination methods. The algorithm was able to efficiently eliminate fifth and seventh harmonics form line current. Simulation and experiments were performed to show the proposed method work in practice. From the the harmonic apparition analysis. mentioned, the measured values are shown that the Total Harmonic Distortion(THD) around 14.27% only. The 3<sup>rd</sup> order harmonics magnitude is only 5.2% and 5<sup>th</sup> order harmonics is 8.2%

#### REFERENCES

- [1] J. N. Chiasson, B. Ozpineci, and L. M. Tolbert, "A five-level three-phase hybrid cascade multilevel inverter using a single DC source for a PM synchronous motor drive," in Proc. IEEE APEC, 2007, pp. 1504-1507.

- [2] J.Vassallo, Nov. 2–6, 2003 "A power-equalized harmonic elimination scheme for utility-connected cascaded H-bridge multilevel converters", in Proc. IEEE Ind. Electron. Soc. Annu. Conf, pp. 1185–1190.

- [3] J. R Wells., Jan. 2007 "Modulation-based harmonic elimination", IEEE Trans. Power Electron., vol. 22, no. 1, pp. 336–340.

- [4] J. Rodriguez, P. W. Hammond, J. Pontt, R. Musalem, P. Lezana, and M. J. Escobar, "Operation of a medium-voltage drive under

- faulty conditions," IEEE Trans. Ind.Electron., vol. 52, no. 4, pp. 1080-1085, Aug. 2005.

- [5] J.Rodriguez, "Multilevel voltage-source-converter topologies for industrial medium voltage drives", IEEE Trans. Ind. Electron., vol. 54, no. 6, pp. 2930–2945, Dec. 2007.

- [6] F. Z. Peng, L. Chen, and F. Zhang, "Simple topologies of PWM ac-ac converters," IEEE Power Electron. Letters, vol. 1, no. 1, pp. 10–13, Mar. 2003.

- [7] Z. Du, L. M. Tolbert, J. N. Chiasson, B. Ozpineci, "A cascade multilevel inverter using a single fuel cell DC source", Proc. IEEE APEC, vol. 1, pp. 426-430, Mar. 2006

- [8] J. Rodriguez, B. Wu, S. Bernet, J. Pontt, and S. Kouro, "Multilevel voltage source-converter topologies for industrial mediumvoltage drives," IEEE Trans. Ind.Electron., vol. 54, no. 6, pp. 2930–2945, Dec. 2014.

- [9] Xu, R.; Yu, Y.; Yang, R.; Wang, G.; Xu, D.; Li, B.; Sui, S. "A Novel Control Method for Transformerless H-Bridge Cascaded STATCOM with Star Configuration". IEEE Trans. Power Electron. 2015, 30, 1189–1202.

- [10] Rahman, M.A.; Islam, M.R. "Modified High Frequency Phase Disposition Pulse Width Modulation for Modular Cascaded Hbridge Multilevel Converters". In Proceeding of the 2017 3rd International Conference on Electrical Information and Communication Technology (EICT 2017), Khulna, Bangladesh, 7–9 December 2017; pp. 1–5.

- [11] Gadalla, A.S.; Yan, X.; Altahir, S.Y.; Hasabelrasul, H. "Evaluating the capacity of power and energy balance for cascaded H-bridge multilevel inverter using different PWM techniques". IET J. Eng. 2017, 1713–1718.